Multiplexer Gate Level . a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. The output gets connected to only one of the n. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which.

from vlsiuniverse.blogspot.com

a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. First multiplexer will act as not gate which. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. The output gets connected to only one of the n. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. implementation of nand, nor, xor and xnor gates requires two 2:1 mux.

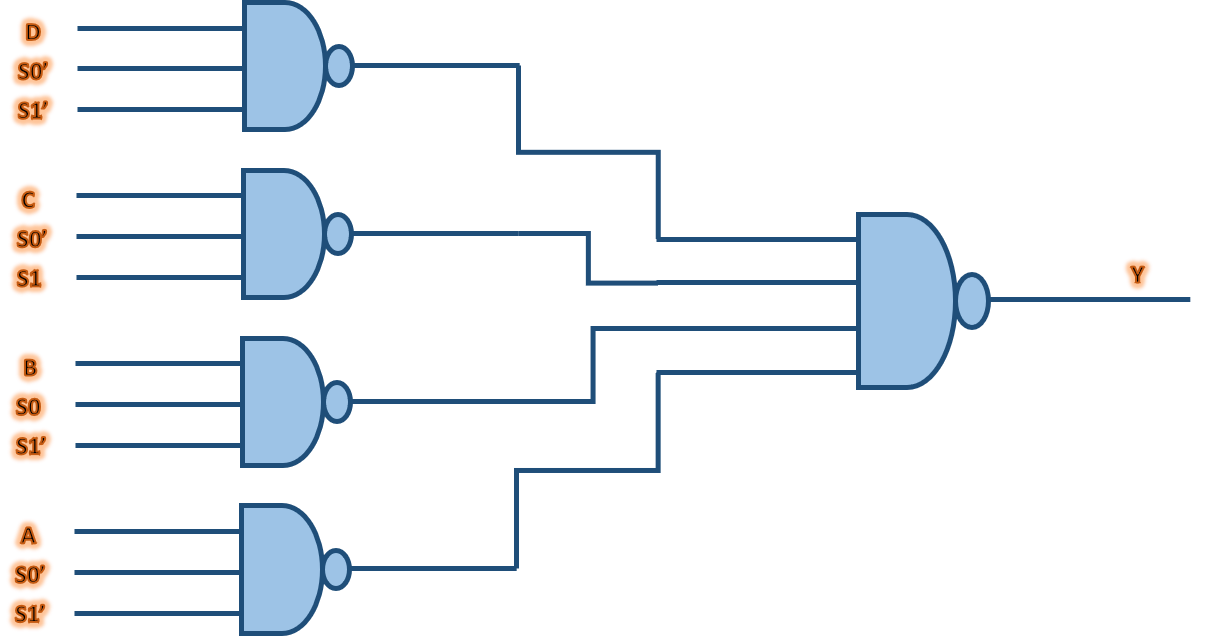

4x1 mux using NAND gates

Multiplexer Gate Level a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. First multiplexer will act as not gate which. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. The output gets connected to only one of the n. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along.

From vlsiuniverse.blogspot.com

4x1 mux using NAND gates Multiplexer Gate Level implementation of nand, nor, xor and xnor gates requires two 2:1 mux. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or. Multiplexer Gate Level.

From www.researchgate.net

41 MUX graphical symbol (a), truth table (b) Download Scientific Diagram Multiplexer Gate Level a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. The output gets connected to only one of the n. First multiplexer will act as not gate which. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. we can use gate. Multiplexer Gate Level.

From courses.cs.washington.edu

Mux implementation using logic gates Multiplexer Gate Level The output gets connected to only one of the n. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. First multiplexer will act as not gate which. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. implementation of nand, nor,. Multiplexer Gate Level.

From circuitenginedundee.z13.web.core.windows.net

Multiplexer Circuit Diagram With Gates Multiplexer Gate Level a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. First multiplexer will. Multiplexer Gate Level.

From alex9ufoexploer.blogspot.com

alex9ufo 聰明人求知心切 21 Multiplexer 多工器 (Gate Level) Multiplexer Gate Level a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or. Multiplexer Gate Level.

From circuitmatthewryansdnq.z4.web.core.windows.net

Alu Circuit Diagram Using Multiplexer Multiplexer Gate Level a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else. Multiplexer Gate Level.

From www.slideserve.com

PPT Multiplexers PowerPoint Presentation, free download ID2666819 Multiplexer Gate Level a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. we can use gate level modeling, we can use. Multiplexer Gate Level.

From www.slideserve.com

PPT Digital Design Using Verilog PowerPoint Presentation, free download ID2747149 Multiplexer Gate Level First multiplexer will act as not gate which. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. . Multiplexer Gate Level.

From www.researchgate.net

Gatelevel circuit design (left) and AST (right) of a 21 multiplexer Download Scientific Diagram Multiplexer Gate Level The output gets connected to only one of the n. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling. Multiplexer Gate Level.

From dxovqrdxz.blob.core.windows.net

What Is A Mux Gate at Joel Putman blog Multiplexer Gate Level The output gets connected to only one of the n. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. we can use gate level modeling, we can use data flow modeling, we. Multiplexer Gate Level.

From slideplayer.com

IV UNIT GATE LEVEL DESIGN ppt download Multiplexer Gate Level First multiplexer will act as not gate which. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. The output gets connected to only one of the n. we can use gate. Multiplexer Gate Level.

From circuitlistdaniela.z19.web.core.windows.net

Transmission Gate Schematic In Cadence Multiplexer Gate Level First multiplexer will act as not gate which. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. The. Multiplexer Gate Level.

From www.researchgate.net

a Multiplexer schematic structure, b truth table of the mux based on... Download Scientific Multiplexer Gate Level we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. First multiplexer will act as not gate which. a complete explanation of the verilog code. Multiplexer Gate Level.

From www.electrical4u.com

Multiplexer What is it? (And How Does it Work) Electrical4U Multiplexer Gate Level The output gets connected to only one of the n. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if. Multiplexer Gate Level.

From www.researchgate.net

DC current path in a CMOS passgate multiplexer as a level shifting... Download Scientific Diagram Multiplexer Gate Level we can use gate level modeling, we can use data flow modeling, we can use ternary operator, we can use if else statement or we can use case. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which. a complete explanation of the verilog code for a. Multiplexer Gate Level.

From www.electroniclinic.com

Multiplexer in Digital Electronics, Block Diagram, Designing, and Logic Diagram Multiplexer Gate Level a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. The output gets connected to only one of the n. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. First multiplexer will act as not gate which. a complete explanation of the verilog. Multiplexer Gate Level.

From vlsiuniverse.blogspot.com

4x1 mux using NAND gates Multiplexer Gate Level implementation of nand, nor, xor and xnor gates requires two 2:1 mux. a complete explanation of the verilog code for a 2x1 multiplexer using gate level,. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. The output gets connected to only one of the n.. Multiplexer Gate Level.

From www.youtube.com

4X1 MULTIPLEXER Using Logic Gates YouTube Multiplexer Gate Level The output gets connected to only one of the n. First multiplexer will act as not gate which. implementation of nand, nor, xor and xnor gates requires two 2:1 mux. a complete explanation of the verilog code for a 8x1 multiplexer (mux) using gate level, dataflow, behavioral, and structural modeling along. a complete explanation of the verilog. Multiplexer Gate Level.